## Home-grown semiconductors for faster, smaller electronics

**Original Published Date:** Monday, August 30, 2021

> [http://www.fleet.org.au/blog/homegrownsemiconductorsforfastersmaller-

Full article electissued by the <u>ARC Centre of Excellence in Future Low-Energy Electronics Technologies</u> [http://www.fleet.org.au] (FLEET).

An ARC-supported study led by University of New South Wales (UNSW)-based <u>FLEET researchers</u> [http://das.showm.c.gov.a a new way of 'growing' electronic components that are ideal candidates for high-frequency, ultra-small electronic devices, quantum dots, and for qubit applications in quantum computing.

Making computers faster requires ever-smaller transistors, with these electronic components now only a handful of nanometres in size. However, in even smaller devices, the channel that the electrons flow through has to be very close to the interface between the semiconductor and the metallic gate used to turn the transistor on and off. Unavoidable surface oxidation and other surface contaminants cause unwanted scattering of electrons flowing through the channel, and also lead to instabilities and noise that are particularly problematic for quantum devices.

Collaborating with a team at Cambridge University who are growing the silicon crystal wafers that form the foundation for these electrical components, the team at UNSW Sydney showed that the problem associated with surface charge can be eliminated by growing a special kind of electrical gate into the chip *before* removing the wafer from the growth chamber.

'In the new work we create transistors in which an ultra-thin metal gate is grown as part of the semiconductor crystal, preventing problems associated with oxidation of the semiconductor surface,' says lead researcher Yonatan Ashlea Alava.

'We have demonstrated that this new design dramatically reduces unwanted effects from surface imperfections, and show that nanoscale quantum point contacts exhibit significantly lower noise than devices fabricated using conventional approaches,' says Yonatan, who is a FLEET PhD student.

The research aligns with aspirations <u>contained in a report</u> induce minimum missioned by the Office of the NSW Chief Scientist & Engineer, Professor Hugh Durrant-Whyte (a former <u>ARC Federation Fellow</u> [http];/whichtidentified/NCGP/Web/Grait opportunities for NSW to increase significantly its contribution to the global semiconductor market.

## Photo credit:

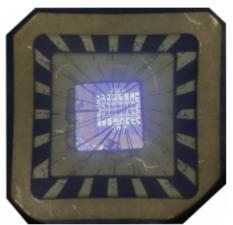

*Electrical characterisation of the new heterostructure device demonstrated greatly reduced surface-charge scattering, and a significant improvement in conductivity. Credit: FLEET.*

Content Last Modified: 30/08/21

Back to top